Riak daya switching tidak dapat dihindari. Tujuan utama kami adalah mengurangi riak keluaran ke tingkat yang dapat ditoleransi. Solusi paling mendasar untuk mencapai tujuan ini adalah menghindari pembentukan riak. Pertama-tama, penyebabnya.

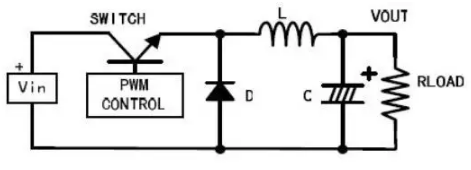

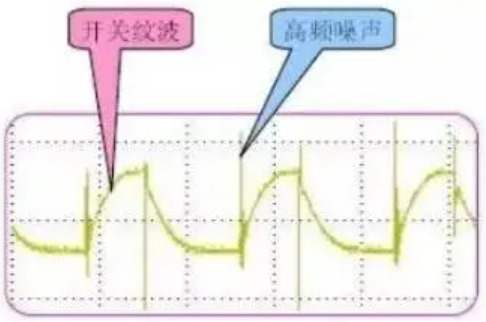

Dengan sakelar pada SWITCH, arus pada induktansi L juga berfluktuasi naik turun pada nilai arus keluaran yang valid. Oleh karena itu, akan terdapat riak dengan frekuensi yang sama dengan Switch pada ujung keluaran. Umumnya, riak pada induktor mengacu pada hal ini, yang berkaitan dengan kapasitas kapasitor keluaran dan ESR. Frekuensi riak ini sama dengan frekuensi catu daya switching, dengan rentang puluhan hingga ratusan kHz.

Selain itu, Switch umumnya menggunakan transistor bipolar atau MOSFET. Apa pun jenisnya, akan ada waktu naik dan turun ketika dinyalakan dan dimatikan. Pada saat ini, tidak akan ada derau di sirkuit yang sama dengan waktu naik dan turun Switch, atau beberapa kali, dan umumnya puluhan MHz. Demikian pula, dioda D berada dalam pemulihan terbalik. Sirkuit ekivalennya adalah rangkaian kapasitor dan induktor resistansi, yang akan menyebabkan resonansi, dan frekuensi deraunya adalah puluhan MHz. Kedua derau ini umumnya disebut derau frekuensi tinggi, dan amplitudonya biasanya jauh lebih besar daripada riak.

Jika konverter AC/DC, selain dua riak (noise) di atas, terdapat juga noise AC. Frekuensinya sama dengan frekuensi catu daya AC input, sekitar 50-60 Hz. Terdapat pula noise co-mode, karena perangkat daya pada banyak catu daya switching menggunakan cangkang sebagai radiator, yang menghasilkan kapasitansi yang setara.

Pengukuran riak daya switching

Persyaratan dasar:

Kopling dengan osiloskop AC

Batas lebar pita 20MHz

Cabut kabel ground probe

1. Kopling AC adalah untuk menghilangkan tegangan DC superposisi dan memperoleh bentuk gelombang yang akurat.

2. Pembukaan batas bandwidth 20MHz bertujuan untuk mencegah interferensi derau frekuensi tinggi dan mencegah kesalahan. Karena amplitudo komposisi frekuensi tinggi besar, amplitudo tersebut harus dihilangkan saat pengukuran.

3. Cabut klip arde probe osiloskop, dan gunakan pengukuran arde untuk mengurangi interferensi. Banyak departemen tidak memiliki cincin arde. Namun, pertimbangkan faktor ini saat menilai apakah alat tersebut memenuhi syarat.

Poin lainnya adalah menggunakan terminal 50Ω. Berdasarkan informasi osiloskop, modul 50Ω berfungsi untuk menghilangkan komponen DC dan mengukur komponen AC secara akurat. Namun, hanya sedikit osiloskop yang memiliki probe khusus seperti itu. Umumnya, probe yang digunakan adalah 100kΩ hingga 10MΩ, yang untuk sementara masih belum jelas.

Hal-hal di atas merupakan tindakan pencegahan dasar saat mengukur riak switching. Jika probe osiloskop tidak langsung terpapar ke titik keluaran, pengukuran harus dilakukan dengan kabel terpilin atau kabel koaksial 50Ω.

Saat mengukur derau frekuensi tinggi, pita penuh osiloskop umumnya berada pada level ratusan mega hingga GHz. Lainnya sama seperti di atas. Mungkin setiap perusahaan memiliki metode pengujian yang berbeda. Pada akhirnya, Anda harus mengetahui hasil pengujian Anda.

Tentang osiloskop:

Beberapa osiloskop digital tidak dapat mengukur riak dengan tepat karena interferensi dan kedalaman penyimpanan. Pada saat ini, osiloskop harus diganti. Terkadang, meskipun bandwidth osiloskop simulasi lama hanya puluhan megabita, kinerjanya lebih baik daripada osiloskop digital.

Penghambatan riak daya switching

Untuk pengalihan riak, secara teoritis dan praktis ada. Ada tiga cara untuk menekan atau menguranginya:

1. Meningkatkan penyaringan induktansi dan kapasitor keluaran

Berdasarkan rumus catu daya switching, besar fluktuasi arus dan nilai induktansi induktansi berbanding terbalik, sedangkan riak keluaran dan kapasitor keluaran berbanding terbalik. Oleh karena itu, peningkatan kapasitor listrik dan keluaran dapat mengurangi riak.

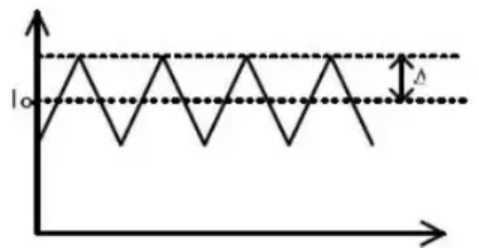

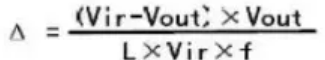

Gambar di atas adalah bentuk gelombang arus pada induktor catu daya switching L. Arus riaknya △ i dapat dihitung dengan rumus berikut:

Dapat dilihat bahwa peningkatan nilai L atau peningkatan frekuensi switching dapat mengurangi fluktuasi arus dalam induktansi.

Demikian pula, hubungan antara riak keluaran dan kapasitor keluaran: VRIPPLE = IMAX/(CO × F). Dapat dilihat bahwa peningkatan nilai kapasitor keluaran dapat mengurangi riak.

Metode yang umum digunakan adalah menggunakan kapasitor elektrolit aluminium untuk kapasitansi keluaran guna mencapai kapasitas besar. Namun, kapasitor elektrolit tidak terlalu efektif dalam meredam derau frekuensi tinggi, dan ESR-nya relatif besar, sehingga kapasitor keramik akan dipasang di sebelahnya untuk mengatasi kekurangan kapasitor elektrolit aluminium.

Pada saat yang sama, ketika catu daya beroperasi, tegangan VIN pada terminal input tetap sama, tetapi arus berubah seiring dengan sakelar. Pada saat ini, catu daya input tidak menyediakan sumber arus, biasanya di dekat terminal input arus (misalnya, tipe buck, dekat sakelar), dan menghubungkan kapasitansi untuk menyediakan arus.

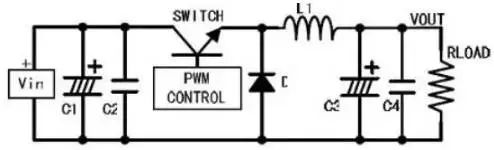

Setelah menerapkan tindakan penanggulangan ini, catu daya sakelar Buck ditunjukkan pada gambar di bawah ini:

Pendekatan di atas terbatas pada pengurangan riak. Karena batasan volume, induktansi tidak akan terlalu besar; kapasitor keluaran meningkat hingga tingkat tertentu, dan tidak ada efek yang nyata dalam mengurangi riak; peningkatan frekuensi switching akan meningkatkan rugi-rugi switching. Jadi, ketika persyaratannya ketat, metode ini kurang efektif.

Untuk prinsip-prinsip switching power supply, Anda dapat merujuk ke berbagai jenis manual desain daya switching.

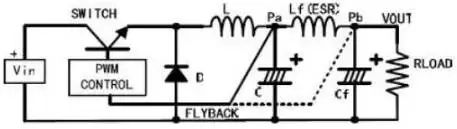

2. Penyaringan dua tingkat adalah menambahkan filter LC tingkat pertama

Efek penghambatan filter LC terhadap riak derau relatif jelas. Berdasarkan frekuensi riak yang akan dihilangkan, pilih kapasitor induktor yang sesuai untuk membentuk rangkaian filter. Umumnya, filter ini dapat mengurangi riak dengan baik. Dalam hal ini, Anda perlu mempertimbangkan titik pengambilan sampel tegangan umpan balik. (Seperti yang ditunjukkan di bawah)

Titik pengambilan sampel dipilih sebelum filter LC (PA), dan tegangan keluaran akan dikurangi. Karena setiap induktansi memiliki resistansi DC, ketika ada arus keluaran, akan terjadi penurunan tegangan pada induktansi, yang mengakibatkan penurunan tegangan keluaran catu daya. Penurunan tegangan ini berubah seiring dengan arus keluaran.

Titik pengambilan sampel dipilih setelah filter LC (PB), sehingga tegangan keluaran sesuai dengan tegangan yang diinginkan. Namun, terdapat induktansi dan kapasitor yang terpasang di dalam sistem daya, yang dapat menyebabkan ketidakstabilan sistem.

3. Setelah output dari catu daya switching, hubungkan penyaringan LDO

Ini adalah cara paling efektif untuk mengurangi riak dan derau. Tegangan keluarannya konstan dan tidak perlu mengubah sistem umpan balik aslinya, tetapi juga paling hemat biaya dan konsumsi dayanya paling tinggi.

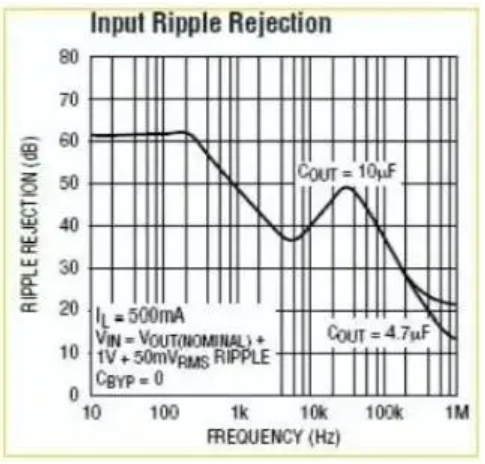

Setiap LDO memiliki indikator rasio peredaman derau. Indikator ini berupa kurva frekuensi-DB, seperti yang ditunjukkan pada gambar di bawah ini, yaitu kurva LT3024.

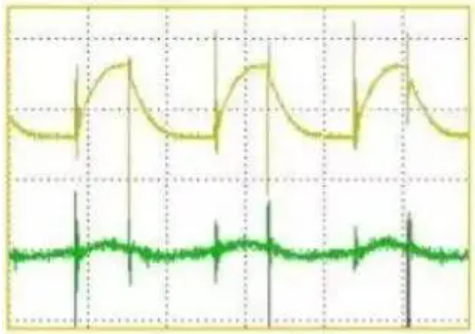

Setelah LDO, riak switching umumnya di bawah 10 mV. Gambar berikut menunjukkan perbandingan riak sebelum dan sesudah LDO:

Dibandingkan dengan kurva pada gambar di atas dan bentuk gelombang di sebelah kiri, terlihat bahwa efek penghambatan LDO sangat baik untuk riak switching ratusan kHz. Namun, dalam rentang frekuensi tinggi, efek LDO tidak begitu ideal.

Mengurangi riak. Pengkabelan PCB catu daya switching juga penting. Untuk derau frekuensi tinggi, karena frekuensi tinggi yang tinggi, meskipun penyaringan pasca-tahap memiliki efek tertentu, efeknya tidak terlalu jelas. Terdapat studi khusus terkait hal ini. Pendekatan sederhananya adalah dengan menggunakan dioda dan kapasitansi C atau RC, atau menghubungkan induktansi secara seri.

Gambar di atas adalah rangkaian ekivalen dioda yang sebenarnya. Ketika dioda berkecepatan tinggi, parameter parasit harus dipertimbangkan. Selama pemulihan balik dioda, induktansi ekivalen dan kapasitansi ekivalen menjadi osilator RC, menghasilkan osilasi frekuensi tinggi. Untuk meredam osilasi frekuensi tinggi ini, perlu menghubungkan kapasitansi C atau jaringan penyangga RC di kedua ujung dioda. Resistansi umumnya 10Ω-100 ω, dan kapasitansinya 4,7PF-2,2NF.

Kapasitansi C atau RC pada dioda C atau RC dapat ditentukan melalui pengujian berulang. Jika tidak dipilih dengan benar, akan menyebabkan osilasi yang lebih parah.

Waktu posting: 08-Jul-2023